# Cascaded H-Bridge Eleven level Inverter Employing PI Control Technique

M.S.Sivagamasundari, Dr.P.Melba Mary, Er.N.K.Jawahar Muthu

Abstract -This paper presents a single phase cascaded h-bridge eleven level inverter topology with a sinusoidal pulse width modulated control scheme. This inverter topology uses two reference signals, instead of one reference signal, to generate PWM signals for the switches. A Proportional Integral controller is used to control this system to get the required output voltage. This topology magnifies the fundamental output voltage with reduction in total harmonic distortion. The proposed system is verified through simulation and the results are compared with the conventional single-phase h-bridge nine-level inverter.

Keywords: Multilevel inverter, Cascaded H-Bridge inverter, Total Harmonic Distortion, PI Controller, Sinusoidal pulse width modulation

#### I. INTRODUCTION

Nowadays Multilevel inverters are drawing attention from researchers and manufacturers due to their more benefits over conventional three level pulse width modulated inverter [PWM] inverters. They offer improved output waveforms, smaller filter size, lower EMI, lower total harmonic distortion (THD), and others [3]-[8].

The three common topologies for multilevel inverters are as follows: 1) diode clamped (neutral clamped) [9]–[11]; 2) capacitor clamped (flying capacitors) [12]–[14] and 3) cascaded H-bridge inverter [15]–[17].

In addition, several modulation and control strategies have been developed or adopted for multilevel inverters, including the following: multilevel sinusoidal (PWM), multilevel selective harmonic elimination, and space-vector modulation [3], [18].

A typical single-phase five-level inverter adopts full-bridge configuration by using approximate sinusoidal modulation technique as the power circuits. The output voltage then has the following five values: zero,  $+1/2V_{dc}$ ,  $V_{dc}$ ,  $-1/2V_{dc}$  and  $-V_{dc}$  (assuming that Vdc is the supply voltage). The harmonic components of the output voltage are determined by the carrier frequency and switching functions. Therefore, their harmonic reduction is limited to a certain degree [25].

**M.S.Sivagamasundari** is currently working as an Assistant Professor in Electrical and Electronics Engineering in V V College of Engineering, Tisaiyanvilai.

**Dr.P.Melba Mary** is working as Principal in V V College of Engineering, Tisaiyanvilai.

N.K.Jawahar Muthu is currently working as an Assistant Executive Engineer in TamilNadu Electricity Board,Tuticorin.

To overcome this limitation, this paper presents a 11 level PWM inverter whose output voltage can be represented in 11 levels: zero, +1/12  $V_{\rm dc}$ , +1/6  $V_{\rm dc}$ , +1/4  $V_{\rm dc}$ , +1/3  $V_{\rm dc}$ , +1/2  $V_{\rm dc}$ , -1/2Vdc, -1/3Vdc, -1/4Vdc, -1/6Vdc and - 1/12Vdc. As the number of output levels increases,the harmonic content can be reduced. This inverter topology uses two reference signals, instead of one reference signal, to generate PWM signals for the

switches.

In this paper, a single-phase cascaded h-bridge multilevel inverter with five H-bridges are proposed. A Sinusoidal PWM control technique is adopted in the firing circuit to provide an acceptable control in the inverter output voltage. PI controller is used to control this system to get the required output voltage. Matlab/Simulink software is used in this work to simulate the power and control circuits. The waveforms of output voltage and current along with the harmonic spectra of output voltage are presented and evaluated.

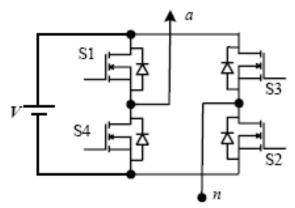

#### II. CASCADED H-BRIDGE MULTILEVEL INVERTER

The structure of single cell of multilevel-cascaded H-bridge configuration is shown in the Fig.1. The output of this cell will have three levels namely +V, 0 and -V. Using one single H-bridge, a three level inverter can be realized. This circuit requires about four switching devices. To realize higher levels of output voltage, the H- bridge circuits are cascaded. The circuit has many advantages like simple, modular, improved waveform which results in reduced total harmonic distortion. This circuit provides high quality output when the number of levels in the output increases and also this reduces the filter components size and cost.

Fig 1. Single cell of multi-level cascaded h-bridge inverter

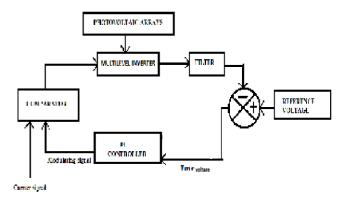

## III. CASCADED H-BRIDGE MULTILEVEL INVERTER WITH PI CONTROLLER

Fig. 2. Cascaded MLI with PI Controller

The Cascaded H-bridge Multilevel inverter with PI controller is shown in Fig. 2. The circuit needs independent dc source which is supplied from the photovoltaic arrays. The gate signals are generated using Sinusoidal pulse width modulation strategy. The output of the cascaded h-bridge eleven level inverter is fed to the load through LC filter to produce sinusoidal output (Vo) which is compared with the reference voltage (Vref) to generate the error signal (e). The input to the PI controller is e. The output of the PI controller i.e the compensating signal (Cs) is added with the reference signal to yield the required modulating signal (ms) which is used to generate the gating pulses. Thus a voltage feedback loop is established to realize the required sinusoidal output voltage. Hence whenever the load is non linear the distortion in the output is more.

## IV. PWM FOR HARMONICS REDUCTION

Several modulation strategies have been developed for multilevel inverters. The most commonly used is the Sinusoidal PWM technique. The Sinusoidal pulse width modulation technique is used here to control the output voltage of the multilevel inverter without affecting the low order harmonics. The modulation technique uses a triangular carrier wave at a high witching frequency is compared with the sinusoidal reference wave at a fundamental output frequency. The intersection between these two signals defines the switching instants of the SPWM pulses.

#### V. SIMULATION RESULTS

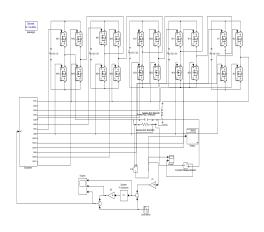

In this paper, the simulation model is developed with MATLAB/SIMULINK. The simulation results of the proposed cascaded h-bridge eleven level inverter is shown in Fig.3. The proposed circuit needs independent dc source which is

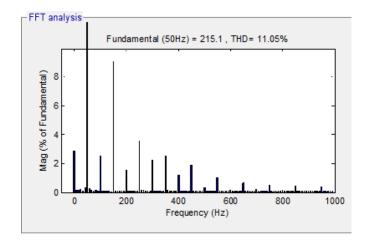

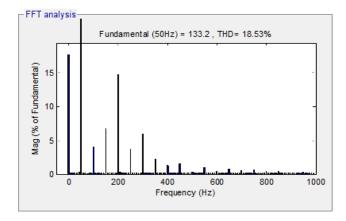

supplied from photovoltaic cell. Simulated output voltage and output current and THD analysis for eleven level cascaded h-bridge inverter is shown in figure 4 and 5. The THD analysis for conventional inverter is shown in figure 6. From the simulated analysis the THD value is low (11.05%) when compared with the conventional single-phase h-bridge nine-level inverter, the THD value is 18.53%.

Fig. 3. Proposed topology

Fig.4.Output voltage and current waveforms

Fig.5.THD analysis (Proposed inverter)

Fig.6.THD analysis (Conventional inverter)

### VI. CONCLUSION

A complete simulation model of a cascaded h-bridge eleven level inverter has been proposed using Matlab/Simulink software. A PI controller is to optimize the performance of the inverter. Sinusoidal PWM control technique is adopted in the firing circuit to provide an acceptable control in the inverter output voltage. Simulation results prove that with this inverter strategy, the low order harmonics are substantially reduced and are compared with that with the conventional single-phase h-bridge nine-level inverter.

#### REFERENCES

- [1] J. M. Carrasco, L. G. Franquelo, J. T. Bialasiewicz, E. Galvan, R. C. PortilloGuisado, M. A. M. Prats, J. I. Leon, and N.Moreno-Alfonso, "Power-electronic systems for the grid integration of renewable energy sources: A survey," *IEEE Trans. Ind. Electron.*, vol. 53, no. 4, pp. 1002–1016, Aug. 2006.

- [2] V. G. Agelidis, D. M. Baker, W. B. Lawrance, and C. V. Nayar, "A multilevel PWMinverter topology for photovoltaic applications," in *Proc.IEEE ISIE*, Guimarães, Portugal, 1997, pp. 589–594.

- [3] S. Kouro, J. Rebolledo, and J. Rodriguez, "Reduced switching-frequencymodulation algorithm for high-power multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 54, no. 5, pp. 2894–2901, Oct. 2007.

- [4] S. J. Park, F. S. Kang, M. H. Lee, and C. U. Kim, "A new single-phase fivelevel PWM inverter employing a deadbeat control scheme," *IEEE Trans. Power Electron.*, vol. 18, no. 18, pp. 831–843, May 2003.

- [5] L. M. Tolbert and T. G. Habetler, "Novel multilevel inverter carrier-based PWM method," *IEEE Trans. Ind. Appl.*, vol. 35, no. 5, pp. 1098–1107, Sep./Oct. 1999.

- [6] M. Calais, L. J. Borle, and V. G. Agelidis, "Analysis of multicarrier PWM methods for a single-phase five-level inverter," in *Proc. 32nd Annu. IEEE PESC*, Jun. 17–21, 2001, vol. 3, pp. 1173–1178.

- [7] N. S. Choi, J. G. Cho, and G. H. Cho, "A general circuit topology of multilevel inverter," in *Proc. 22nd Annu. IEEE PESC*, Jun. 24–27, 1991, pp. 96–103.

- [8] G. Carrara, S. Gardella, M. Marchesoni, R. Salutari, and G. Sciutto, "A new multilevel PWMmethod: A theoretical analysis," *IEEE Trans. Power Electron.*, vol. 7, no. 3, pp. 497–505, Jul. 1992.

- [9] A. Nabae and H. Akagi, "A new neutral-point clamped PWM inverter," *IEEE Trans. Ind. Appl.*, vol. IA-17, no. 5, pp. 518–523, Sep./Oct. 1981.

- [10] J. Pou, R. Pindado, and D. Boroyevich, "Voltage-balance limits in fourlevel diode-clamped converters with passive front ends," *IEEE Trans. Ind. Electron.*, vol. 52, no. 1, pp. 190–196, Feb. 2005.

- [11] S. Alepuz, S. Busquets-Monge, J. Bordonau, J. Gago, D. Gonzalez, and J. Balcells, "Interfacing renewable energy sources to the utility grid using a three-level inverter," *IEEE Trans. Ind. Electron.*, vol. 53, no. 5, pp. 1504–1511, Oct. 2006.

- [12] T. Meynard and H. Foch, "Multi-level choppers for high voltage applications," *Eur. Power Electron. J.*, vol. 2, no. 1, pp. 45–50, Mar. 1992.

- [13] D.-W. Kang, B.-K. Lee, J.-H. Jeon, T.-J. Kim, and D.-S. Hyun, "A symmetric carrier technique of CRPWM for voltage balance method of flying capacitor multilevel inverter," *IEEE Trans. Ind. Electron.*, vol. 52, no. 3, pp. 879–888, Jun. 2005.

- [14] B.-R. Lin and C.-H. Huang, "Implementation of a threephase capacitorclamped active power filter under unbalanced condition," *IEEE Trans. Ind. Electron.*, vol. 53, no. 5, pp. 1621– 1630, Oct. 2006.

- [15] M. Marchesoni, M. Mazzucchelli, and S. Tenconi, "A non conventional power converter for plasma stabilization," in *Proc. IEEE Power Electron. Spec. Conf.*, 1988, pp. 122–129.

- [16] J. Rodriguez, P. Hammond, J. Pontt, R. Musalem, P. Lezana, and M. Escobar, "Operation of a medium-voltage drive under faulty conditions," *IEEE Trans. Ind. Electron.*, vol. 52, no. 4, pp. 1080– 1085, Aug. 2005.

- [17] X. Kou, K. Corzine, and M. Wielebski, "Overdistention operation of cascaded multilevel inverters," *IEEE Trans. Ind.Appl.*, vol. 42, no. 3, pp. 817–824, May/Jun. 2006.

- [18] J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multicarrier PWM strategies for multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 724–738, Aug. 2002.

- [19] M. Calais, V. G. Agelidis, and M. S. Dymond, "A cascaded inverter for transformerless single phase grid-connected

# International Journal of Advanced Research in Electronics and Communication Engineering (IJARECE) Volume 3, Issue 4, April 2014

- photovoltaic systems," in *Proc. 31st Annu. IEEE PESC*, Jun. 18–23, 2001, vol. 3, pp. 1173–1178.

- [20] M. H. Rashid, Power Electronics: Circuits, Devices, and Applications, 3rd ed. Englewood Cliffs, NJ: Prentice-Hall, 2004.

- [21] N. Mutoh and T. Inoue, "A control method to charge series connected ultraelectric double-layer capacitors suitable for photovoltaic generation systems combining MPPT control method," *IEEE Trans. Ind. Electron.*, vol. 54, no. 1, pp. 374–383, Feb. 2007.

- [22] T. Esram and P. L. Chapman, "Comparison of photovoltaic array maximum power point tracking techniques," *IEEE Trans. Energy Convers.*, vol. 22, no. 2, pp. 439–449, Jun. 2007.

- [23] N. Femia, G. Petrone, G. Spagnuolo, and M. Vitelli, "Optimizing dutycycle perturbation of P&O MPPT technique," in *Proc. 35th Annu. IEEE PESC*, Jun. 20–25, 2004, vol. 3, pp. 1939–1944.

- [24] X. Liu and L. A. C. Lopes, "An improved perturbation and observation maximum power point tracking algorithm for PV arrays," in *Proc. IEEE 35th Annu. PESC*, Jun. 20–25, 2004, vol. 3, pp. 2005–2010.

- [25] Jeyraj Selvaraj and Nasrudin A. Rahim, "Multi level inverter for grid connected pv system employing digital pi controller" IEEE TRANSACTIONS ON Industrial Electronics, Vol. 56, No. 1, Jan 2000

ISSN: 2278 - 909X