# Design of Auto Depannage Digital System with Efficient Fault Coverage

### Archanalakshmi K.S<sup>1</sup>, Arathy Iyer R<sup>2</sup>

<sup>1</sup>M.Tech VLSI & Embedded Systems, SNGCE, <sup>2</sup>Assistant Professor, ECE, SNGCE

Abstract— In this paper presents the design of an efficient method for fault recovering in a digital system. The biological inspiration used in auto depannage system overcomes the limitations of conventional fault tolerant methods. The fault recovering and processing steps are adopted from endocrine cellular communication. By using this method system can recover fault by replacing faulty module with spare module or with transferring the encoded data in similar module. This scheme reduces hardware overhead and additional rerouting along with increasing size of the circuit.

Index Terms—Endocrine cellular communication, Functional layer, Gene control layer, Stem Cell, Working cell

#### I. INTRODUCTION

Every electronic circuit always faces the difficulty of functional fault, even if they provide good performance. The regular routine of the circuit may disturb if there any single fault occur in the system. In critical applications, fault plays a major role in system performance, and system need efficient fault recovery method to maintain normal state. In the early stages, conventional methods like DMR and TMR were used ,but they offered less fault coverage and increased redundancy. Thus new approaches arose from biological concepts and are more suitable in fault tolerant digital system design [1]-[15]. One of the delegate approaches, MUX TREE method [13] offers better self repairing and replication, but has only less fault coverage. Another approach uses endocrine systems [9] to improve redundancy, but needs a complex communication for rerouting. This paper presents a new methodology to overcome these problems, thereby using endocrine cellular communication for self repairing [1] in digital systems. The Auto Depannage mechanism improves the fault detection and also reduces hardware overhead for digital system design.

## II. AUTO DEPANNAGE MECHANISM USING ENDOCRINE CELLULAR COMMUNICATION

Auto Depannage digital system is a self recovering digital system that can recover from different types of functional faults. In endocrine cellular communication, endocrine cell secretes a specific hormone for cell replacement only after it

ISSN: 2278 - 909X

receives another specific hormone of damage cell indication. By adopting the similar mechanism, proposed system isolates the faulty cells and replaces with a proper spare cell.

#### III. SYSTEM OVERVIEW

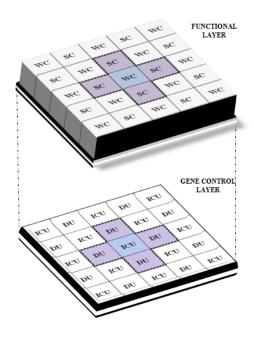

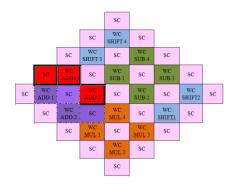

The entire architecture of Auto Depannage digital system is composed of two layers, called functional layer and gene control layer as in Fig 1.

Fig 1. Auto Depannage digital system architecture

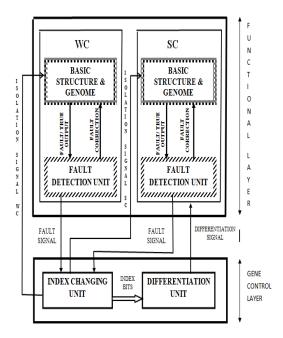

Both layers are operated in parallel, thus the system can recover even several faults occur in different modules a same time. Functional layer contain artificial cells (modules). Module may be working cell(WC), spare cell(SC) or isolated cells. Every WC is surrounded with its 4 SC as shown in Fig 1, and each SCs is connected to its neighbouring WC. Each WC having its own ICU and SCs has it own DU in gene control layer. The gene control layer is functionally positioned in parallel with the functional layer. Thus, the gene control layer must control the functional layer properly without a collision. Fig 2. shows interaction between layers for fault recovering. Here WC is replaced by SC when a permanent fault arises in it.

Fig 2. Interaction between layers for fault recovery

#### A. Functional Layer

Functionality of target digital system is divided into different genome and fed in each working cells (WC). Each WC is surrounded by its own stem (spare) cells and it contains genome of neighboring working cell. The isolated cells are cells which are isolated due to permanent fault . These 3 types of cells are commonly known as module. All modules have similar basic structure and these different modules forms a layer called functional layer (structural layer). Every module contain two major units. They are,

#### 1) Genome and Basic Structure

The genome plays the most important role in each cell. Genome is similar to a memory, which contains encoded data about functionality and routing structure. Using the proper genome, module constructs a basic structure corresponding to functionality of WC. The output from it is given to fault detection and correction unit.

#### 2) Fault Detection and Correction Unit

The drawbacks of existing system are it requires large memory for fault detection and correction, and less functional fault recovery. The proposed architecture overcomes it by elementary operational unit as shown in Fig 3. The elementary unit produce bitwise fixed result corresponding to inputs of WC. This result is fed into comparator unit 1 and cross check the data in (True or fault output). Then it is set flag if any mismatch is present. Faulty data and its location, is found out by using comparator unit 2. If it is a transient fault, then try to correct it using elementary unit and perfect genome and send corrected data to cell. If the fault appears simultaneously, even after fault correction and genome replacement, then it is a permanent fault. It is due to the fault in genome, the entire cell has to be replaced then set a fault signal and given to gene control layer.

ISSN: 2278 - 909X

Fig 3. Fault detection and correction unit

#### B. Gene Control Layer

The gene control layer assigns proper spare cell by producing control signals after receiving fault signal as in Fig 2. It finds available spare cell and selects proper genome to the particular spare cell. Then the spare cell takes the functionality of the faulty working cell. The gene control layer is composed of,

#### 1) Index Changing Unit

Index changing unit (ICU) receives faulty signals and changes the index bits. TABLE I shows index bits and its ideal values.

State bit: It shows whether the cell is a SC or a WC or an isolated cell.

Direction bit: It indicates the direction of the WC for which stem cell is differentiated

Differentiation bit: It signifies the indication to enable spare cell.

TABLE I . INDEX BITS FOR EACH STEM CELL

| State bit               | Stem cell  Working or Isolated cell                            |       | 0  |

|-------------------------|----------------------------------------------------------------|-------|----|

|                         |                                                                |       | 1  |

| Direction bits          | The direction of the WC for which stem cell is differentiate d | Left  | 00 |

|                         |                                                                | Down  | 01 |

|                         |                                                                | Right | 10 |

|                         | u                                                              | Up    | 11 |

| Differentiatio<br>n bit | No change                                                      |       | 0  |

|                         | Differentiate the stem cell                                    |       | 1  |

## International Journal of Advanced Research in Electronics and Communication Engineering (IJARECE) Volume 3, Issue 9, September 2014

#### 2) Differentiation Unit

The Differentiation Unit (DU) receives index bits and sends differentiated signal to corresponding stem cell. At the same time, the isolation signal is sent to faulty module from ICU. Thereby, the fault recovery is achieved and the target system maintains the normal operation

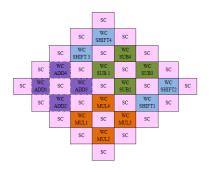

#### IV. FUNCTIONAL FAULT COVERAGE

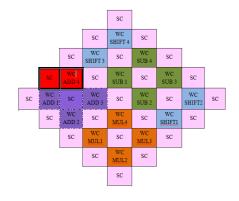

Auto Depannage mechanism offers functional fault coverage. It may be a transient or permanent or simultaneous fault. Fig 4 shows Auto Depannage ALU without any fault. Consider it can perform 4 different operations like addition, subtraction, multiplication and shifting. The WC and SC arranged as in Fig 4.

Fig 4. Auto Depannage ALU without any fault

#### A. Transient Fault

Transient fault or a temporary fault can recover by fault detection and correction unit itself.

#### B. Permanent Fault

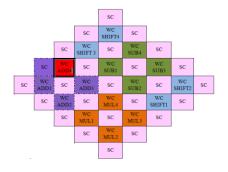

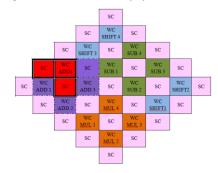

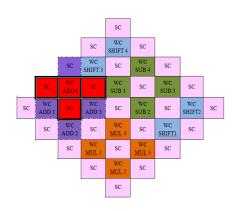

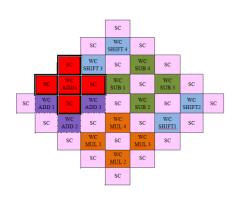

Permanent fault corrupt the genome or its basic structure. Thus it can recover by selecting proper spare and isolates faulty cell. Consider the case of selecting addition operation. If there is no fault in adder WC's, the system continue it's working in without using SCs as in Fig 4. But when the adder 4 WC suffer by temporary fault, it will try to overcome by fault detection and correction unit and retain it's working condition. Sometimes it is not possible correct the fault, due to permanent fault in genome. Thus the WC replaced by stem cells and also isolated the faulty cell. Gene control layer generate corresponding signals according to the status of functional layer. The following figures, Fig 5 to Fig 9 show different stages of fault recovering in Auto Depannage ALU.

Fig 5. Permanent fault recovery by left SC

ISSN: 2278 - 909X

Fig 6. Permanent fault recovery by down SC

Fig .7 Permanent fault recovery by right SC

Fig 8. Permanent fault recovery by top SC

Fig 9 . Permanent fault in adder 4 WC and its all SCs

If 4 SCs and its working cell WC ADD4 become fault, the addition operation module stop its working by isolating SCs as in Fig 9. Thus the adder 4 unit becomes fault.

#### C. Simultaneous Fault

There is a chance to occur simultaneous fault in this ALU. Here the Fig 10. shows the simultaneous fault occurring in working cell of WC ADD3 and left stem cell of WC ADD4.SC for both cell are same. In that case gene control layer assigns the next proper stem cell to WC ADD4, that is its down cell, as in Fig 10. These are shows only several conditions of fault in adder cell. Similarly it is possible to recover different kinds of faults in other functional modules in Auto Depannage ALU .

Fig 10. Simultaneous fault recovery.

#### V. SIMULATION RESULT

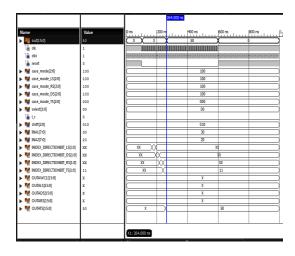

Fig 11. Simulation result of system after fault recovery.

ISSN: 2278 - 909X

Fig 11, shows the permanent fault recovery after injecting fault in WC and its 3 SCs.

#### VI. EXPERIMENTAL SETUP

The proposed system is embedded in a digital platform with an Xilinx Spartan 6 FPGA for the application of an ALU. Several cases of recovery from a permanent fault and transient fault are demonstrated in the platform. When the transient fault is detected, at the rising of the next clock faulty data recovered to normal data and the system operates normally.

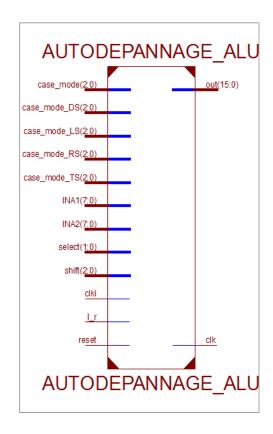

Fig 12. Autodepannage ALU

In permanent fault, the normal operation is maintained using spare cells. Fig.5 to Fig 10 shows the changed states of cells by the fault recovery after a fault is injected in cells. Here, the system repairs the permanent fault in a counter clockwise sequence. However, if the fault is generated in TS after a faulty RS is replaced by TS, the entire system stops operating because there is no SC left for repair. The speed of the clock used for the recovery is much faster. Thus, the ALU can operate normally after fault generation. Through various demonstrations, the proposed system is verified.

#### VII. PERFORMANCE ANALYSIS WITH EXISTING APPROACHES

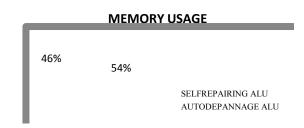

The main aim of the proposed Autodepannage architecture is to reduce the area, memory usage, time delay and thereby increase scalability and accuracy. Xilinix ISE Design Suite 14.2 platform provides a summary for logic utilization, time constraints and memory usage. By analysing the graphs we can conclude that compare to existing self repair ALU, proposed Autodepannage ALU reduce the area, memory usage, time delay.

Fig 12. Memory Usage

Fig 13. Timing analysis

Fig 14. Area Analysis

ISSN: 2278 - 909X

Here the Fig.12 shows proposed Auto Depannage ALU reduce in memory usage existing self repair ALU. This will happen mainly due to the modified architecture of Fault detection and correction. Timing Analysis shows in Fig.13, the proposed system reduces the total time delay. It is the sum total of logic time and the routing time. The total time required to Auto Depannage ALU got reduced. Area Analysis Fig 14 shows that the proposed system reduces the

total area compared to the existing one. These 3 Plots were drawn by analysing the design summary of both approaches after synthesis. The proposed system was compared to other major self-repair approaches and it was found that the proposed system has good fault coverage, low overhead, and no unutilized resources for fault recovery.

#### VIII. CONCLUSION AND FUTURE SCOPE

The Auto Depannage digital system provides good scalability and fault coverage. New architecture for fault detection offers less memory usage and having good fault coverage. Furthermore, due to the new architecture, the cells could be arranged in densely and flexible way, also the WC could be expanded to any four directions. The exact control in the gene-control layer offers fault recovery without collision. As a result, all these create the system efficient compare to other existing approaches.

For further improvement of the proposed Auto Depannage system, there remains several issues awaiting further studies. The primary goal of developing a fault tolerant or Auto Depannage system is to deal with faults that can occur in the target system. Other faults that might occur in additional hardware are not considered. Hence, the secondary faults that can occur in the additional functional hardware should be considered as well in the consideration of the cost and frequency. This means that addressing possible faults in the additional functional hardware remains as a topic for further study.

#### ACKNOWLEDGMENT

I would like to acknowledge the support of the Department of Electronics and Communication Engineering, SNGCE for technical facilities. I am also grateful to my beloved guide, Ms. Arathy Iyer R. (Assistant Prof., SNGCE), for her valuable contributions and encouragement which make this work successful. Last but not the least; I humbly extend my gratitude to other faculty, my friends and family especially Ms. Ann Varghese, for her unending support. Above all, I thank God Almighty for giving me strength, courage and blessings to complete this work.

#### REFERENCES

- [1] Isaak Yang, Sung Hoon Jung, and Kwang-Hyun Cho," Self Repairing Digital System With Unified Recovery Process Inspired by Endocrine Cellular Communication"- IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, JUNE 2013

- [2] M. Samie, G. Dragffy, and T. Pipe, "UNITRONICS: A novel bioinspired fault tolerant cellular system," in Proc. NASA/ESA Conf. Adapt. Hardw. Syst., Jun. 2011, pp. 58–65.

- [3] M. Samie, G. Dragffy, and T. Pipe, "Bio-inspired self-test for evolvable fault tolerant hardware systems," in Proc. NASA/ESA Conf. Adapt. Hardw. Syst., Jun. 2010, pp. 325–332.

- [4] M. Samie, G. Dragffy, A. Popescu, T. Pipe, and C. Melhuish, "Prokaryotic bio-inspired model for embryonics," in Proc. NASA/ESA Conf. Adapt. Hardw. Syst., Jul.—Aug. 2009, pp. 163—170.

- [5] M. Samie, G. Dragffy, A. Popescu, T. Pipe, and J. Kiely, "Prokaryotic bio-inspired system," in Proc. NASA/ESA Conf. Adapt. Hardw. Syst., Jul.—Aug. 2009, pp. 171–178.

- [6] W. Barker, D. M. Halliday, Y. Thoma, E. Sanchez, G. Tempesti, and A. M. Tyrrell, "Fault tolerance using dynamic reconfiguration on the POEtic

## International Journal of Advanced Research in Electronics and Communication Engineering (IJARECE) Volume 3, Issue 9, September 2014

- tissue," IEEE Trans. Evol. Comput., vol. 11, no. 5, pp. 666–684, Oct. 2007.

- [7] P. K. Lala, B. K. Kumar, and J. P. Parkerson, "On self-healing digital system design," Microelectron. J., vol. 37, no. 4, pp. 353–362, Apr. 2006.

- [8] S. Mitra, N. Seifert, M. Zhang, Q. Shi, K. S. Kim, "Robust System Design with Built-In Soft-Error Resilience," Computer, vol. 38, no. 2,pp. 43-52, February 2005.

- [9] A.J. Greensted and A.M.Tyrrell, "An endocrinologic-inspired hardware implementation of a multicellular system," in Proc. NASA/DoD Conf. Evolvable Hardw., 2004, pp. 245–252.

- [10] X. Zhang, G. Dragffy, A. G. Pipe, N. Gunton, and Q. M. Zhu, "A reconfigurable self-healing embryonic cell architecture," in Proc. ERSA, Jun. 2003, pp. 134–140.

- [11] P. K. Lala and B. K. Kumar, "An architecture for self-healing digital systems," J. Electron. Testing: Theory Appl., vol. 19, no. 5, pp. 523–535, Oct. 2003.

- [12] Mange, M. Sipper, A. Stauffer, and G. Tempesti, "Toward robust integrated circuits: The embryonics approach," Proc. IEEE, vol. 88,no. 4, pp. 516–541, Apr. 2000.

- [13] Mange, E. Sanchez, A. Stauffer, G. Tempesti, P. Marchal, and C. Piguet, "Embryonics: A new methodology for designing fieldprogrammable gate arrays with self-repair and self-replicating properties," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 6, no. 3, pp. 387–399, Sep. 1998.

- [14] Ortega and A. Tyrrell, "Design of a basic cell to construct embryonic arrays," IEE Proc. Comput. Digital Tech., vol. 145, no. 3, pp. 242–248, May 1998.

- [15] Mange, S. Durand, E. Sanckez, A. Stauffer, G. Tempesti, P. Marchal, and C. Piguet, "A new paradigm for developing digital systems based on a multi-cellular organization," in Proc. IEEE Int. Symp. Circuits Syst.,vol. 3. Apr.—May 1995, pp. 2193–2196.

Archanalakshmi K.S received her B.Tech Degree in Electronics and Communication from SNGCE ,Ernakulam in 2008 and pursuing M.Tech (VLSI and Embedded systems) Degree from the same college. Her areas of interest are digital circuits,VLSI Design, Embedded System etc.

**Arathy Iyer R** presently working as assistant professor in SNGCE, Ernakulam

ISSN: 2278 - 909X